Analisar as intruções do tipo B;

Esboçar o fluxo de dados para atender a essas instruções;

Criar o FD em VHDL.

As instruções do tipo B:

São utilizadas para executar desvios condicionais na execução do programa;

Possuem o mesmo opcode e utilizam o Funct3 para diferenciar entre elas (beq, bne, blt, etc …);

Possuem dois campos de registradores: Rs1 e Rs2, que são comparados;

Possuem dois campos que formam o valor imediato:

Esse valor, de 12 bits, está codificado na instrução;

E representa um inteiro com sinal.

A instrução desse tipo, para a nossa implementação básica, é:

O formato das instruções do tipo B são uma variação do formato das instruções do tipo S, por isso, também é chamado de SB.

Desvia Se Igual (branch equal: beq)

Compara o conteúdo de dois registradores definidos na instrução (Rs1 e Rs2). Se forem iguais, desvia para o endereço definido por PC+extSinal(imediato). Caso contrário, continua na próxima instrução.

O imediato é um inteiro com sinal. Como ele sofre um deslocamento para a esquerda, significa que o valor indica, em número de pares de bytes, o total de desvio que ocorrerá. Isso implica que a distância de desvio será de 4 KBytes para a frente ou para trás.

| imediato[12|10:5] | Rs2 | Rs1 | funct3 | imediato[4:1|11] | opcode |

|---|---|---|---|---|---|

| 7 bits | 5 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| MSB (b31) | LSB (b0) |

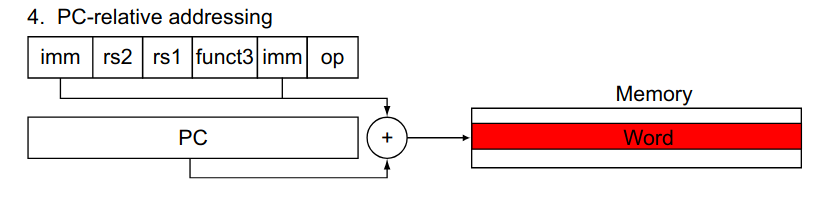

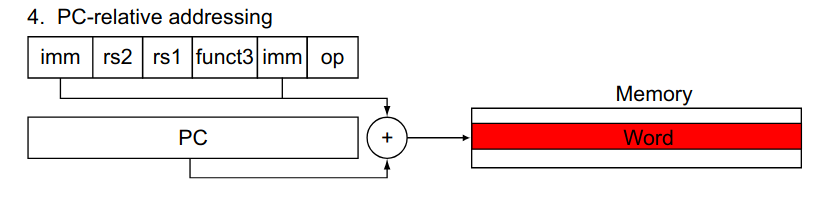

Para formar o valor de 32 bits que será somado ao PC, o imediato tem seu sinal extendido e é deslocado um bit para esquerda, conforme mostrado abaixo:

O imediato deve ser montado a partir dos bits distribuidos nos campos do imediato de 7 bits e imediato de 5 bits. Note que a sequência dos bits não está em ordem, permitindo economizar MUXes em implementações mais simples.

A reordenação do imediato deve ser feita no componente de Geração do Imediato.

O significado dos nomes dos campos:

Opcode: Contém o código, com 7 bits, da instrução: neste caso 0x67;

Rs1: O endereço do primeiro registrador que será comparado;

Rs2: O endereço do segundo registrador que será comparado;

imediato[4:1|11]: Cinco bits utilizados para formar o imediato;

funct3: Seleciona qual o tipo de comparação que deve ser feito (igual, menor, maior, etc…);

imediato[12|10:5]: Sete bits utilizados para formar o imediato.

Sintaxe:

Sua operação:

Se x[r7] = x[r8] então:

Caso contrário:

O modo de endereçamento dessa classe de instruções é o Relativo ao PC.

Para a instrução:

INICIO: # A posição de memória de INICIO está 5 instruções antes do BEQ.

...

...

...

...

...

beq r7, r8, INICIO;Qual seria a sua codificação?

| Imediato[12|10:5] | Rs2 | Rs1 | funct3 | Imediato[4:1|11] | opcode |

|---|---|---|---|---|---|

| 7 bits | 5 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 31~25 | 24~20 | 19~15 | 14~12 | 11~7 | 6~0 |

A instrução em assembly define o endereço de destino como sendo 5 instruções antes, ou seja, 20 bytes. Para voltar devemos somar o valor -20 ao PC. Esse valor, em complemento de dois, é:

Em binário, com 32 bits: 1111 1111 1111 1111 1111 1111 1110 1100 (0xFFFFFFEC)

Precisamos calcular o imediato que, após convertido, resulte em 0xFFFFFFEC.

O primeiro passo é transformar esse valor para 13 bits. Teremos:

O segundo passo é desfazer o deslocamento para a esquerda. Isso é feito através de um deslocamento para a direita. Assim, teremos o valor de 12 bits do imediato:

Imediato, com 12 bits = 1111 1111 0110

Consultando o greencard:

Opcode: 0b110_0111 (0x67);

Rs1: x7 = 0b0_0111 (0x7);

Rs2: x8 = 0b0_1000 (0x8);

funct3: 0b000 (0x0);

Utilizando o valor do imediato obtido, vamos fazer a reordenação dos bits:

Imediato[4:1|11]: 0b01101

Imediato[12|10:5]: 0b111_1111

| Imediado(11:5) | Rs2 | Rs1 | funct3 | Imediato[4:1|11] | opcode |

|---|---|---|---|---|---|

| 7 bits | 5 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 1111111 | 01000 | 00111 | 000 | 01101 | 1100111 |

| 31~25 | 24~20 | 19~15 | 14~12 | 11~7 | 6~0 |

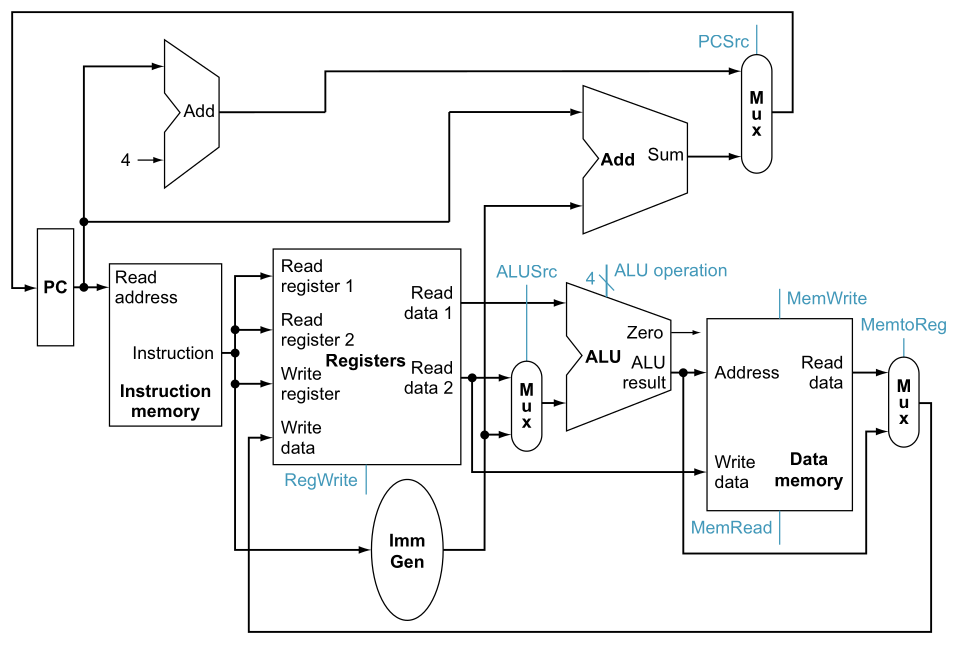

Faça a análise da instrução beq:

Descreva o funcionamento RTL da arquitetura para implementá-la;

Esboce o caminho de dados;

Simule o funcionamento da instrução;

Se não estiver bom, reinicie o processo.

Com o caminho de dados pronto, passe para a implementação em VHDL e testes.

Quando estiver funcional:

Mescle com o caminho de dados das instruções do tipo R, I e S:

Para iniciar, use o fluxo de dados das instruções anteriores como referência.

Esta atividade será parte da entrega intermediária.

A ULA pode ser a mesma do fluxo de dados para as intruções do tipo R (soma e subtração).

Para o teste, temos que criar um pequeno programa que utilize as instruções do tipo B.

Procedimento:

No VHDL, fazer as conexões:

Dos pontos de controle às chaves e aos LEDs (ou utilizar uma Unidade de Controle Simplificada).

Do clock e do reset do Program Counter aos botões, utilizando um discriminador de borda para cada botão.

Da saída e entrada do PC para um MUX. A saída desse MUX será conectada aos displays de 7 segmentos (fazer a ligação direta dos decodificadores sem utilizar registradores). A seleção do MUX será feita através das chaves da placa.

Usando os botões, será possível executar o programa uma instrução por vez e reiniciar a execução.

Esta Atividade é a consolidação das Instruções do tipo R, I, S e B. Ela deverá ser entregue através do Blackboard!