Analisar as intruções do tipo I e S;

Esboçar o fluxo de dados para atender a essas instruções;

Criar o FD em VHDL.

Não possuem só uma opção para o campo de opcode, como as do tipo R;

Possuem dois campos de registradores: Rd e Rs1;

Possuem um campo com um valor imediato:

Esse valor, de 12 bits, está codificado na instrução;

E representa um inteiro com sinal.

São utilizadas para:

Carregar valores imediatos (constantes) nos registradores;

Fazer operações lógicas e aritméticas com valores imediatos, por exemplo:

As instruções desse tipo, para a nossa implementação básica, são:

Formato das instruções do tipo I:

| Imediato | Rs1 | funct3 | Rd | opcode |

|---|---|---|---|---|

| 12 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 31~20 | 19~15 | 14~12 | 11~7 | 6~0 |

| MSB (b31) | LSB (b0) |

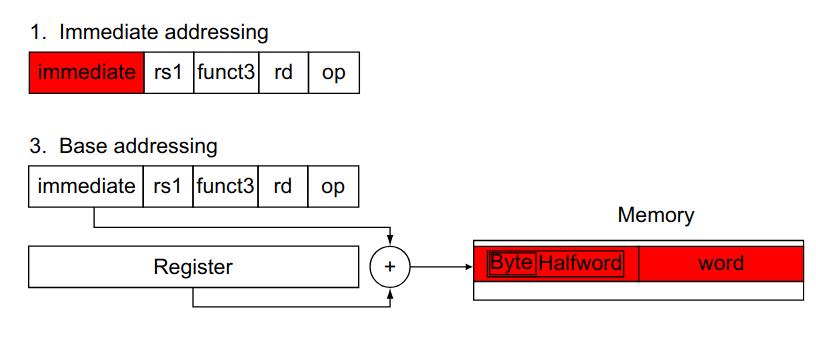

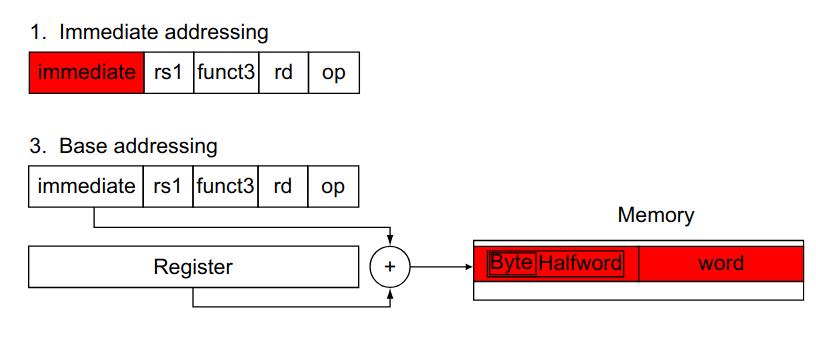

O modo de endereçamento usado nas instruções do tipo I está na figura abaixo.

São utilizadas para transferir o conteúdo do banco de registradores para a memória principal;

Possuem o mesmo opcode e utilizam o Funct3 para diferenciar entre elas (sw, sh e sb);

Possuem dois campos de registradores: Rs1 e Rs2;

Possuem dois campos que formam o valor imediato:

Esse valor, de 12 bits, está codificado na instrução;

E representa um inteiro com sinal.

A instrução desse tipo, para a nossa implementação básica, é:

Exemplo de Store Word:

Organização dos campos para o formato S:

| Imediado(11:5) | Rs2 | Rs1 | funct3 | Imediado(4:0) | opcode |

|---|---|---|---|---|---|

| 7 bits | 5 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 31~25 | 24~20 | 19~15 | 14~12 | 11~7 | 6~0 |

| MSB (b31) | LSB (b0) |

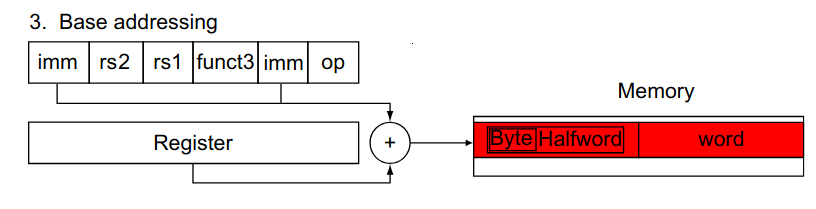

O modo de endereçamento usado nas instruções do tipo S está na figura abaixo.

Sintaxe:

Operação:

x[rd] = M[x[rs1]+extSinal(imediato)]

Onde:

extSinal = { 20{imediato[11]}, imediato }

Ou seja, o valor de 32 bits utilizado na soma terá nos seus 20 bits mais significativos a repetição do bit 11 do imediato (o bit de sinal) e os próximos 12 bits serão o próprio imediato.

Sintaxe:

Operação:

M[x[rs1]+extSinal(imediato)] = x[rs2]

Onde:

extSinal = { 20{imediato[11]}, imediato }

A formação do imediato de 12 bits é feita pela concatenação do Imediado(11:5) com o Imediado(4:0). Esse valor tem o seu bit de sinal extendido da mesma forma que na instrução lw.

Para saber a codificação utilizada nos campos das instruções, consulte o greencard.

Para a instrução:

Qual seria a sua codificação?

| Imediado(12) | Rs1 | funct3 | rd | opcode |

|---|---|---|---|---|

| 12 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 31~20 | 19~15 | 14~12 | 11~7 | 6~0 |

lw: x[rd] = M(x[rs1] + extSinal(imediato)).

Consultando o greencard:

Opcode: 0b000_0011 (0x3);

Rs1: x2 = 0b0_0010 (0x2);

Rd: x1 = 0b0_0001 (0x1);

funct3: 0b010 (0x2);

Convertendo 1000 para binário: 0d1000 = 0b0011 1110 1000 (0x3E8)

| Imediado(11:0) | Rs1 | funct3 | Rd | opcode |

|---|---|---|---|---|

| 12 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 0011 1110 1000 | 00010 | 010 | 00001 | 0000011 |

| 31~20 | 19~15 | 14~12 | 11~7 | 6~0 |

Para saber a codificação utilizada nos campos das instruções, consulte o greencard.

Para a instrução:

Qual seria a sua codificação?

| Imediado(11:5) | Rs2 | Rs1 | funct3 | Imediado(4:0) | opcode |

|---|---|---|---|---|---|

| 7 bits | 5 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 31~25 | 24~20 | 19~15 | 14~12 | 11~7 | 6~0 |

sw: M(x[rs1] + extSinal(imediato)) = x[rs2].

Consultando o greencard:

Opcode: 0b010_0011 (0x23);

Rs1: x2 = 0b0_0010 (0x2);

Rs2: x1 = 0b0_0001 (0x1);

funct3: 0b010 (0x2);

Convertendo 1000 para binário: 0d1000 = 0b0011 1110 1000 (0x3E8)

Imediado(4:0): 0b01000

Imediado(11:5): 0b001_1111

| Imediado(11:5) | Rs2 | Rs1 | funct3 | Imediado(4:0) | opcode |

|---|---|---|---|---|---|

| 7 bits | 5 bits | 5 bits | 3 bits | 5 bits | 7 bits |

| 0011111 | 00001 | 10001 | 010 | 01000 | 0100011 |

| 31~25 | 24~20 | 19~15 | 14~12 | 11~7 | 6~0 |

Responder o quiz de participação, no blackboard, em:

Conteúdos > Participação > Aula_13_Quiz-P1

Faça a análise das instruções anteriores:

Na sequência:

Descreva o funcionamento RTL da arquitetura;

Esboce o caminho de dados;

Simule o funcionamento de cada instrução (utilizando papel e lápis);

Com o caminho de dados pronto:

Quando estiver funcional:

Mescle com o caminho de dados para as instruções do tipo R;

Implemente no kit de desenvolvimento;

E faça os testes necessários.

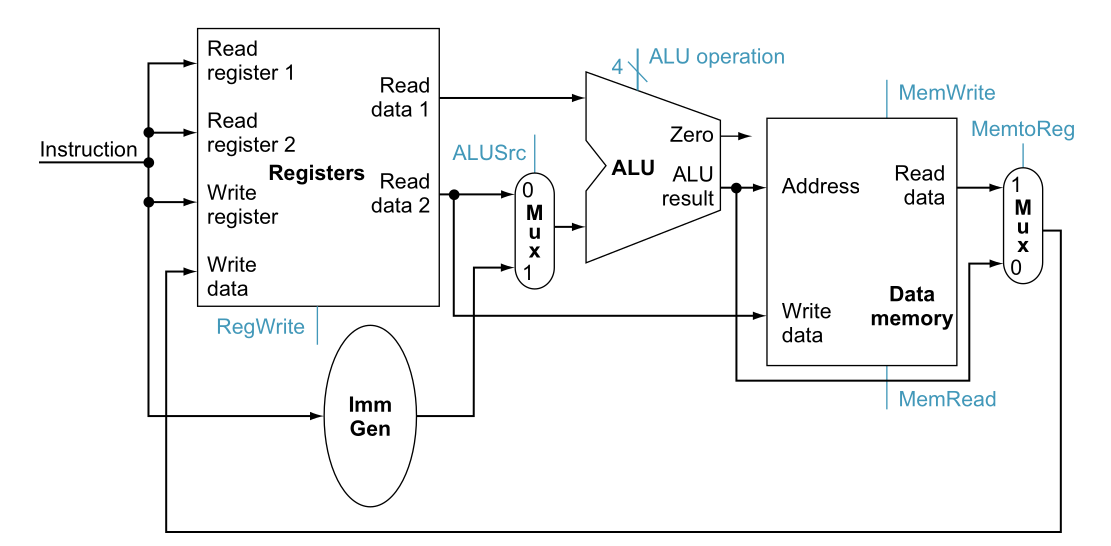

Solução do fluxo de dados para lw e sw:

Esta atividade será parte da entrega intermediária.

Para facilitar, a ULA pode ser a mesma do fluxo de dados para as intruções do tipo R (soma e subtração).

Para o teste, temos que criar um pequeno programa que utilize as instruções do tipo I.

Procedimento:

No VHDL, fazer as conexões:

Dos pontos de controle às chaves (ou utilizar uma Unidade de Controle Simplificada).

Do clock e do reset do Program Counter aos botões, utilizando um discriminador de borda para cada botão.

Da saída da ULA, da entrada de dados na RAM e da saída da RAM para um MUX. A saída desse MUX será conectada aos displays de 7 segmentos (fazer a ligação direta dos decodificadores sem utilizar registradores) e aos 8 LEDs (de 0 até 7) - ver esquema na aba de projetos. A seleção do MUX será feita através das chaves da placa.

Usando os botões, será possível executar o programa uma instrução por vez e reiniciar a execução.

Esta Atividade deverá ser entregue através do Blackboard!